Three engineers. Two co-inventors. One engineering system.

The VENDOR engineering team consists of three engineers with complementary deep specializations in system-level architecture, industrial power electronics, and FPGA-based control logic. Two team members are co-inventors of the core patent family. The team operates close to intellectual property generation, control logic and safety system design, high-voltage and impulse electronics regimes, and long-cycle validation and TRL progression. All operational results are validated at TRL 5–6 with 1,000+ cumulative operational hours including extended continuous operation cycles.

Co-inventors of patent: WO2024209235 (PCT, 37 countries) · ES2950176 (granted, Spain)

Engineering Accountability Over Biography

In deep-tech energy systems operating near certification, IP governance, and high-voltage hardware boundaries, the correct representation of a team is not biography — it is functional accountability and demonstrable engineering output.

We don’t present personalities.

We present accountability.

VENDOR operates at the intersection of high-voltage hardware, nonlinear control logic, and system-level intellectual property under active patent examination across six jurisdictions. In this context, functional accountability is the correct representation — not personal biography.

Demonstrable output,

not narrative.

What matters at this stage is what has been built, how it has been validated, and what is being carried forward toward independent third-party verification. The people on this page are identified by engineering role, responsibility domain, and measurable contribution.

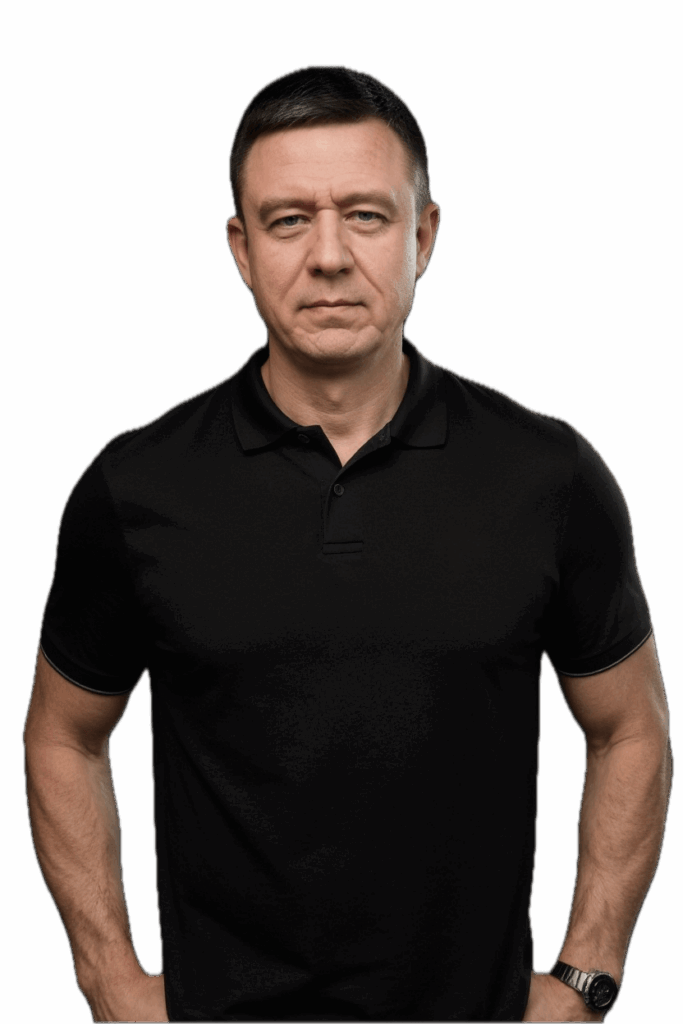

Vitaly Peretyachenko

Co-Founder & CEO

Systems Architecture · Infrastructure Strategy · Applied Engineering

LinkedIn →Engineering Background

Systems responsible for human safety must be deterministic, verifiable, and failure-aware.

Vitaly’s professional background spans medicine, IT infrastructure, and large-scale system engineering. Early work in intensive care and surgical environments established a foundational principle: a system at the boundary of human safety cannot tolerate non-deterministic behavior.

Alongside clinical practice, he developed early telemedicine tools and digital health systems, later transitioning into infrastructure-scale engineering and system orchestration. At VENDOR, this posture governs every architectural decision across the TRL 5→6 validation pathway.

Key Technical Competencies

VENDOR Responsibility

- Architectural coherence — ensuring every subsystem evolves toward a verifiable, certifiable, and scalable whole

- Definition of validation logic and testability boundaries across all TRL stages

- Long-term IP strategy — co-inventor of patent family WO2024209235 (PCT, 37 countries)

- Integration of engineering, regulatory, and economic constraints into a unified architecture framework

- Alignment of engineering milestones with investor-facing and certification timelines

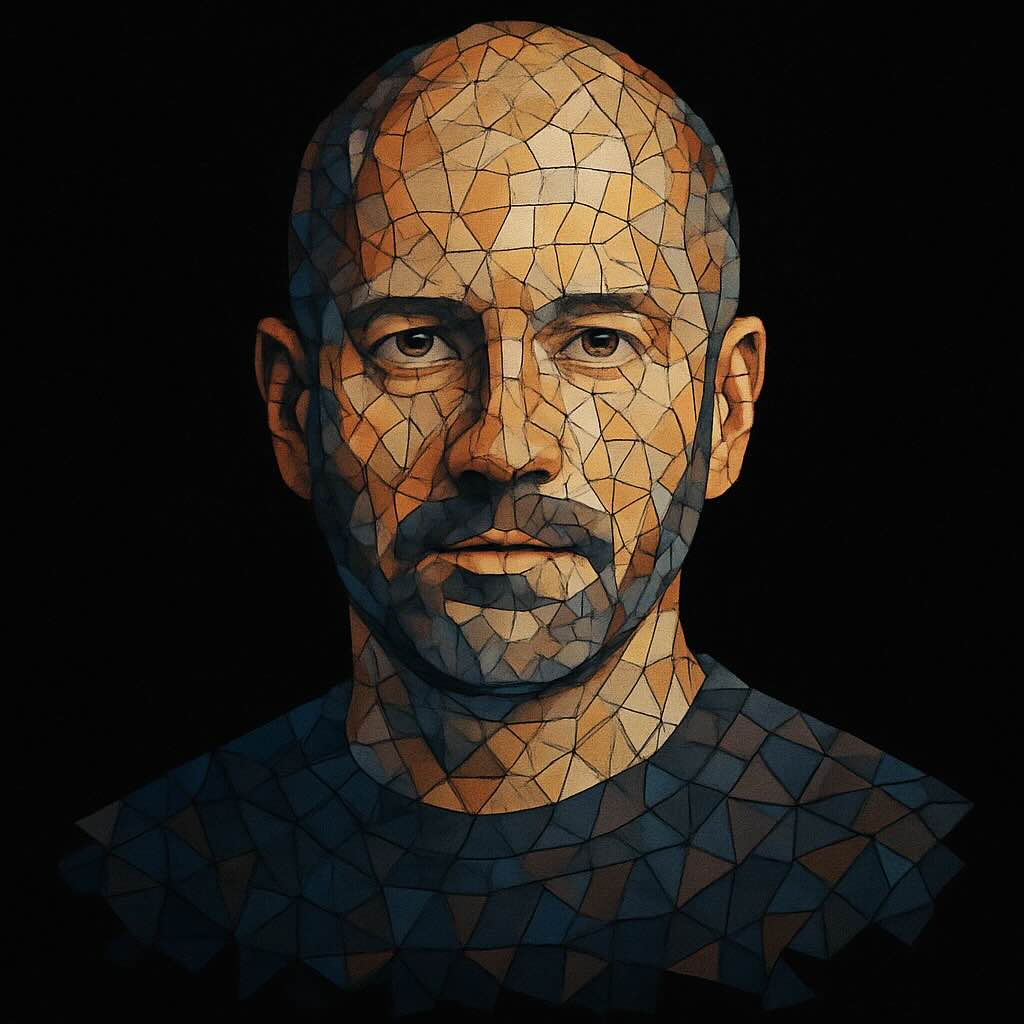

Oleg Krishevich

Co-Founder & CTO

Power Electronics · Control Systems · Industrial Architecture

LinkedIn —Engineering Background

Power-stage instability translates directly into equipment loss. Control errors cannot be masked by software abstraction.

Oleg specializes in industrial power electronics and control systems for environments where failure tolerance is minimal and system behavior must remain predictable under load, stress, and long-term operation. His background includes design and deployment of power systems in continuous-duty and mission-critical applications — where electrical stability, thermal margins, and control reliability are primary engineering constraints.

Before VENDOR, Oleg worked on systems where power-stage instability directly translated into equipment loss, maintenance windows were strictly limited, and control logic had to remain transparent — not obscured by software layers that could mask physical failure. This discipline defines the VENDOR control architecture.

Key Technical Competencies

VENDOR Responsibility

- Overall power-system architecture and electrical topology of the autonomous power node

- Control logic governing pulse generation and operating regime formation

- Safety interlocks, protection strategies, and fault-response sequences

- Scalability design for multi-module configurations (2.4–24 kW range)

- Alignment between physical electrodynamic behavior and control-layer assumptions

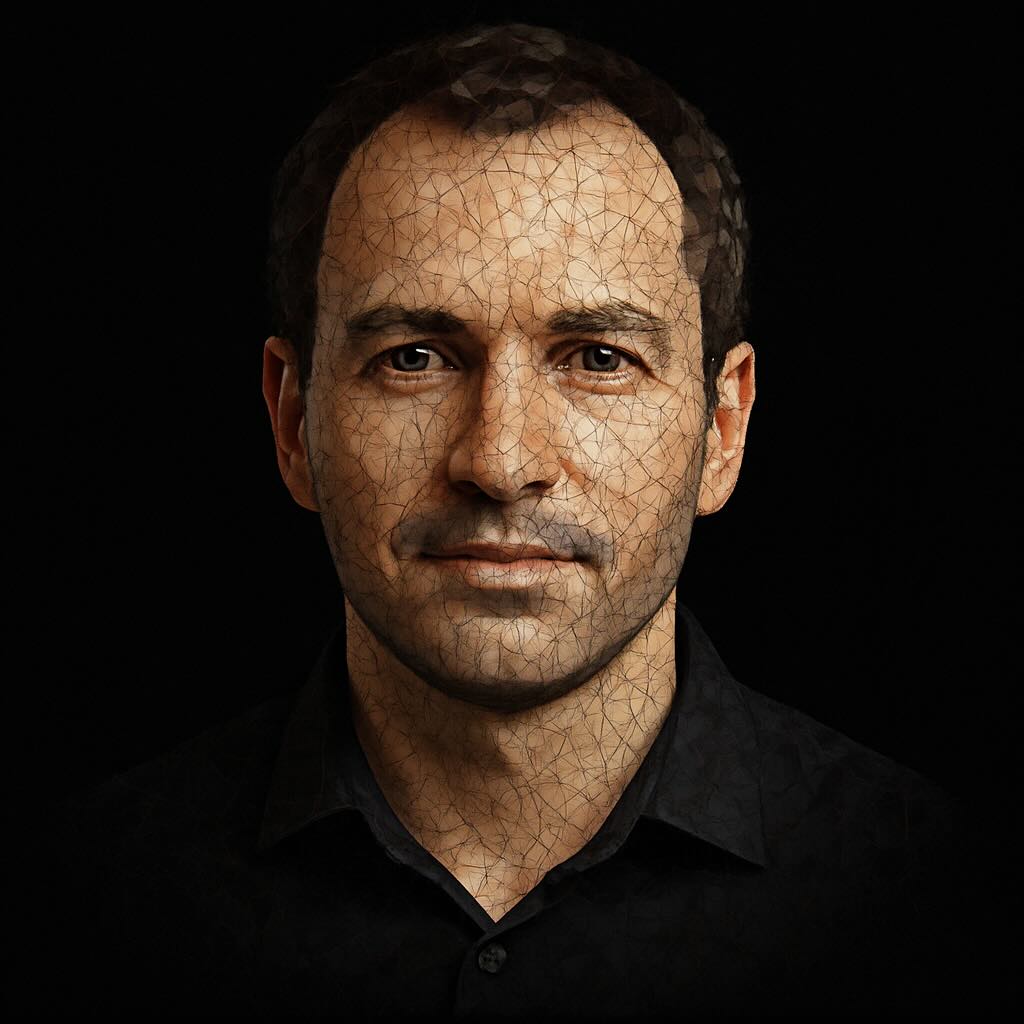

Oleg Shnaider

System Architect

High-Speed Electronics · FPGA · Power Circuit Design

LinkedIn —Engineering Background

Component tolerances directly affect system survival. Latency and jitter cannot be abstracted away.

Oleg is a system-level hardware architect specializing in high-speed electronics, FPGA-based control logic, and precision power circuitry. His engineering background is centered on systems operating near physical and electrical limits — where timing accuracy, signal integrity, and deterministic behavior are critical constraints, not optimization targets.

Before VENDOR, Oleg worked on industrial modules where component tolerances directly affected system survival, hardware behavior had to precisely match theoretical models under stress, and no software layer could compensate for hardware-level timing failures. This context is the foundation for his role in VENDOR’s control and synchronization architecture.

Key Technical Competencies

VENDOR Responsibility

- Low-level hardware architecture of control and synchronization blocks

- FPGA logic governing multi-module coordination and real-time regime monitoring

- Precision timing and threshold handling in pulse-resonant operating regimes

- Ensuring electrical behavior remains deterministic across all defined operating envelopes

- Critical intersection of physics, electronics, and control theory — the layer where the regime is either maintained or lost

Built for Hard Problems

01

Stability under uncertainty

The engineering target is deterministic behavior under real load, thermal variation, and operating envelope stress — not just under controlled laboratory conditions.

02

Failure modes assumed before they appear

Every subsystem is designed against its own failure — not discovered after the fact. This posture originates from environments where failure during operation is not a recoverable event.

03

Behavior validated, not narratives

Operational hours, regime stability data, and independent third-party review define what has been achieved. Unmeasured claims carry no weight in architecture decisions.

04

Safety as a first-class requirement

Certification constraints and safety boundaries are built into architecture from the earliest design decisions — not retrofitted before submission.

1,000+ operational hours — including extended continuous operation cycles — is the current measurable answer to whether this team can carry the technology forward at TRL 5–6. The ongoing pathway toward DNV/TÜV independent verification is the next milestone.

Read the Engineering ManifestoEvaluation and Partnership Paths

For Engineers and Due Diligence

Request Technical Evaluation

Operational data. Patent documentation. Energy balance methodology. Validation pathway. NDA-protected technical Q&A with the engineering team.

→ Request EvaluationFor Investors and Strategic Partners

Access Silent Pitch Room

EVCI structure. Market model. Design Partner pathway. Milestone-gated funding triggers. Co-inventor team available for deep-dive sessions.

→ Silent Pitch RoomFor Partnerships and Pilot Programs

Explore Pilot Program

Telecom · AI / Edge infrastructure. Off-grid critical systems · Industrial applications. Discuss deployment architecture with the team.

→ Explore Pilot Program